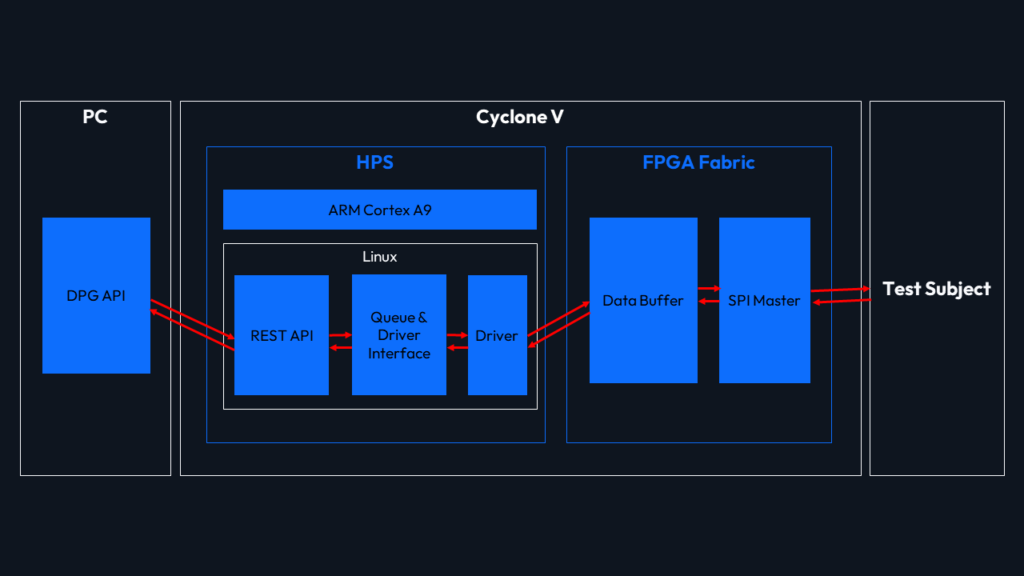

COMPONENTS

The components of DPG

DPG API

- Enables the creation of data objects

- Sends and receives test data to the DPG

- Transfers a bunch of test data bundled together in a STL-container

- Analyses/compares the received data with expected data

- Integratable in existing test automation environments

- Written in C++ (ISO C++ 14 Standard)

REST API

- Sends & receives data from the DPG API

- Forwards the data to the software queues

- Updates the configuration of the ip cores

- Checks the states of the hardware interfaces

- Easily extendable to support additional hardware components

- Written in Rust

Queue & Driver Interface

- One queue for every component

- Buffers data until the hardware is ready

- Ensures that all requests are processed in the correct order

- Uses the linux device drivers to access the hardware

- Written in Rust

Linux Device Driver

- Data transfer with char device

- Setting and reading configuration values with sysfs

- Only one user access (mutex locked)

- No data loss due data buffering with a FIFO

(Read can be performed asynchronous) - Written in C

Data Buffer

- Soft IP Core (in FPGA Fabric)

- Double Buffer

- Buffers all data for the SPI Master

- Configurable via a memory mapped Interface

- Interrupt-Functionality

- Written in VHDL

SPI Master

- Soft IP Core (in FGPA Fabric)

- Generates SPI Signals

- Bidirectional communication

- Receives data from the data buffer

- Configurable via a memory mapped Interface

- Written in VHDL

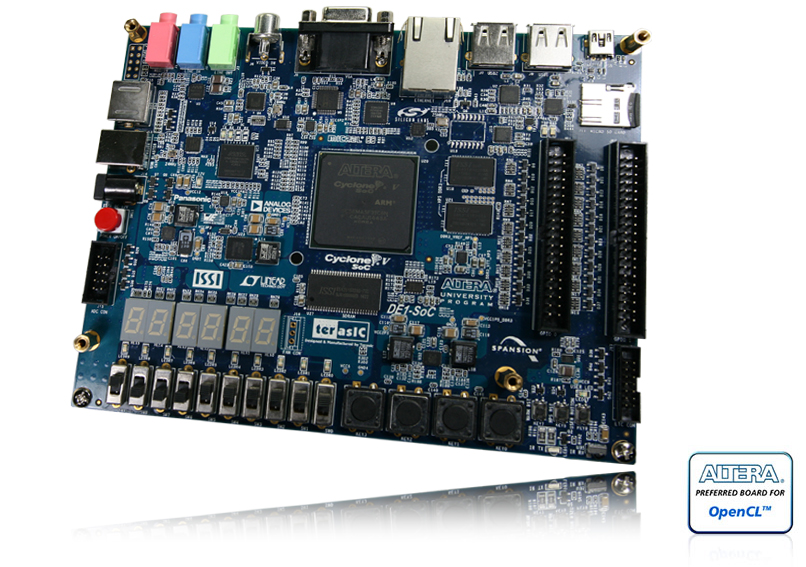

Directly usable with the Terasic DE1-SoC Board

DPG was initially developed based on the Terasic DE1-Soc Board.

That means you can simply deploy DPG on this board and start generating signals.

Nevertheless it’s still possible to use DPG on your custom boards.